## HDL DESIGN FOR ULTRA HIGH MULTI FREQUENCY CLOCK RATE-MULTI CHANNEL PRBS UNIVERSAL DATA SCRAMBLER DESCRAMBLER ASIC IP CORE

#### PROF P.N.V.M SASTRY

J.B.R.E.C., Dean-R&D-CELL & ECE, Hyderabad, India, shastrypnvm@gmail.com

#### PROF.G.KRISHNAIAH

J.B.R.E.C., Professor – ECE, Hyderabad, India, Krishh786@gmail.com

#### PROF.DR.D.N.RAO

J.B.R.E.C., Principal, Hyderabad, India, PRINCIPAL JBR@YAHOO.COM

#### DR S.VATHSAL

J.B.I.E.T., Dean- R&D&EEE, Hyderabad, India, svathsal@gmail.com

ABSTRACT: Scrambler De-Scrambler is a device used to encode and decode the message data in to randomized(Seed words) data.. This paper deals Design of High Speed Multichannel Universal Data Scrambler De-ScramblerOf Different Data Rates (Giga/Tera Bit Rate) for Ultra High Speed Wireless Applications like Gigabit WIMAX,WIFI,3G,4G,Parallel Data Computing, Internet, Cloud Computing etc. Scrambling Different PRBS Data as perCCITT – ITU Standards. This Design consists of Different Pattern Sequence based PRBS Generators & XOR Gates for encryption and decryption of digital data either serially/parallel. Design using Xilinx ISE 9.2i Software,Programming done by using VHDL & Verilog HDL, Design Implementation on Latest Xilinx Spartan III FPGA Kit.

**KEYWORDS:** Gbps – Giga Bits Per Second, Tbps- Tera Bits Per Second, Wi-Fi- Wireless Fidelity , PRBS- PseudoRandom Binary Sequence, CCITT- Consulting Committee for International Telegraph and Telephone, FPGA-FieldProgrammable Gate Array, ISE- Integrated Software Environment, VHDL– Very High Speed Integrated CircuitHardware Description Language.

### INTRODUCTION

In Modern Digital Communication Systems and Applications, Products, Scrambler-Descrambler very important component for encryption and decryption of randomized digital data In the form seed words in cipher text format Basically this universal data scrambler designed by using Linear Feed Back Shift Register and XOR gates. The length of Universal Scrambler is 2<sup>n</sup>-1. Scrambling done at the transmitter side for encryption of digital data and descrambling done at the receiver side for decryption of Randomized Digital Data. For Implementation of Different Communication Protocols, Scrambling and Descrambling Reduce the Noise in the Data Codes, Error Rate of Transmission and Reception. Scrambler - Descrambler IP Cores are Very Suit for HiFi-Hitech Smart Computing wireless Communication Products likeWi-Fi, Gi-Fi, WCDMA, CDMA, 3G,4G Wireless Communication Products, Wireless Network On Chip Transceivers, Wireless Network Routers. GPS,GSM,GPRS, Bus Communication Network Protocols. Max. Transceivers, OFDMA Transceivers.

#### **Notations:**

$D = Delay \ element, S = Scrambler \ Input, D^xS = A \ sequence \ S \ delayed \ by \ x \ bits, m, \ n = Length \ of registers, T1 = Scrambler \ Output, T2 = Descrambler \ Input, R1, R2 = Registers$

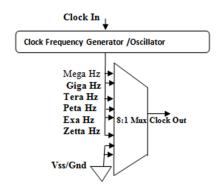

#### Multi Clock Frequency Generator / Oscillator

Figure 1.Ultra High Multi Clock Frequency Generator

**Description**—Multi Clock Frequency Generator consists Clock Frequency Generator/Oscillator, 8:1 Multiplexer. Clock Frequency Generator . Generator consists Counter to Generates Different Clock Frequencies, MHz,GHz,THz,PHz,EHz,ZHz of 10<sup>6</sup> or 2<sup>20</sup>, 10<sup>9</sup> or 2<sup>30</sup>, 10<sup>12</sup> or 2<sup>40</sup>, 10<sup>15</sup> or 2<sup>50</sup>, 10<sup>18</sup> or 2<sup>60</sup>, 10<sup>21</sup> or 2<sup>70</sup> Clock Cycles. 8:1 Multiplexer Selects The one the above frequencies to generate Baud Rate of Specific Clock. Frequencies to Scrambler /Descrambler ASIC IP Core for High Speed Wireless Data Security Products.

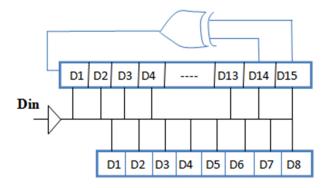

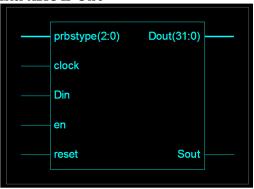

#### Scrambler ASIC IP Core/Generator

Figure 2. Scrambler Block Diagram

**Description**— Scrambler Design Consists Multi Clock Frequency Generator and LFSR-Linear Feed back Shift Register, Data Register and Data input is in XOR with LFSR Feedback output Generates Scrambler Output for Wireless Data Security Products/ Applications.

#### Sequence of LFSR and Data Values for Scrambler

**Description**—Data Values/Bits in the Data Register and LFSR Random sequence Patterns (Seed Words) are XOR'ed and generates Scrambler Design output for Encrypting the Data of Plain Text to Cipher Text Format.

Figure 3. Sequence Of LFSR and Data in Values in the Scrambler

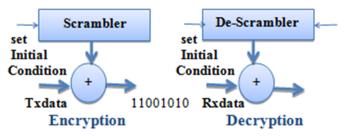

#### **Encryption/Decryption**

Figure 4. Data Encryption Decryption using Scrambling Descrambling

**Description**—Data encryption Encoding and Data Decryption Decoding Done by Scrambler and De-Scrambler IP Core Generator.

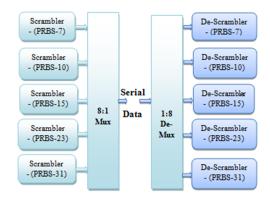

# HIGH SPEED MULTICHANNEL SCRAMBLER DE-SCRAMBLER DESIGN ARCHITECTURE AS PER ITU STANDARDS

### Description

The Design Architecture Consists of Data Selector / De-selector (Mux/De-Mux) for selecting and Deselecting Different Scrambled Descrambled PRBS Data Sequence Patterns (Seed Words) of Different Data Rates as per CCITT ITU Standards. Scrambled / De-Scrambled Data Sequences PRBS-7, 10,15,23,31 pattern sequences XORed with Data Register Pattern. The Data Selector is used synchronize different randomized data sequence frames. Data Selector selects different Scrambled Data Sequences of Different PRBS Pattern sequences 7, 10,15,23,31 by XORed with Data Register and send the scrambled data serially through serialized link. De-serialize the data sequence frames by using De-multiplexer as a De-selector to distribute the Descrambled data to original message data by Decrypting.

Figure 5. High Speed Multi Channel Scrambler-De-Scrambler Design Architecture

## SIMULATION WAVE FORM REPORTS

## **Simulation-Scrambler ASIC IP Core**

Figure 6. Scrambler IP Core

## **MultiChannel Scrambler IP Core**

Figure 7. Multichannel Scrambler IP Core

# Serial Scrambler IP Core

Figure 8. Serial Scrambler ASIC

# **DESIGN FLOW REPORTS**

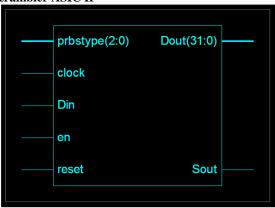

# RTL Design Block Scrambler ASIC IP

Figure 9. Scrambler ASIC

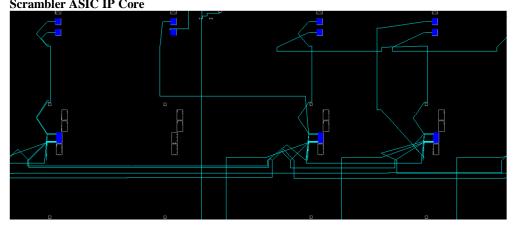

## **RTL Schematic Scrambler ASIC IP Core**

Figure 10. Schematic Of Scrambler ASIC

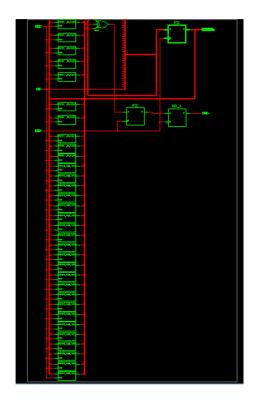

# FPGA Placed Design Report Scrambler ASIC IP Core

Figure 11. Scrambler ASIC Placed Design Report

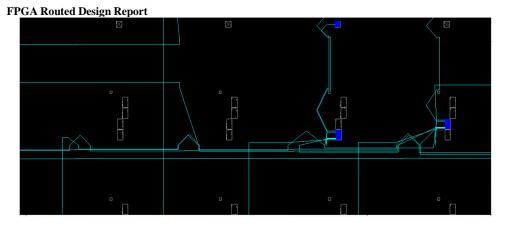

# FPGA Routed Design Report Scrambler ASIC IP Core

Figure 12. Scrambler ASIC Routed Design

# DESIGN FLOW REPORT-DE-SCRAMBLER ASIC IP CORE

# RTL Block - De-Scrambler ASIC IP Core

Figure 13. De-Scrambler ASIC RTL Block

## **RTL Schematic**

Figure 14. De-Scrambler ASIC Schematic

## **FPGA Placed Design Report**

Figure 15. De-Scrambler ASIC Placed Design

Figure 16. De-Scrambler ASIC Routed Design

## **ACKNOWLEDGEMENTS**

We discussed and cooperated with each other lot for generation of the design. I am very thankful to my supervisor Dr.S. Vathsal, and also to Dr.D.N.Rao in all aspects.

#### **CONCLUSION**

This design is very suit for Data Accuracy and Speed of High Speed wireless Application Products like WIFI, Internet, and Cloud etc The main intention of designing scrambler and De-Scrambler is for reduction of noise for getting accurate signal data by data encryption and decryption of different PRBS Pattern Sequences.

#### REFERENCES

Wikipedia, "http:en.wikipedia.org/wiki/Scrambler"

Springer, "http://link.springer.com/article/10.1007%2Fs10791-012-9212-1#page-1"

Rajib Imran and Monirul Islam Embedded, FPGA based, VLSI and ASIC Designs, June 2013,e-ISSN: 2321-6980 "Industrial Modified Digital scrambler & Descrambler system"

G.M. Bhat, M. Mustafa, Shabir Ahmad and Javaid Ahmad, Vol.2 No. 10 (Oct 2009) "VHDL Modeling and Simulation Of Data Scrambler and Descrambler For Secure Data Communication"

Ghulam M .Bhatt, Muhammad Mustafa, Shabir A. Parah, Javaid Ahmad ,2010," Field programmable gate array (FPGA) implementation of novel complex PN-code generator based data scrambler and descrambler".

#### **BIBLIOGRAPHY**

Prof.P.N.V.MSastry Currently working with a Capacity of Dean- IT EDA Software – R&D CELL & ECE DEPARTMENT, He Did Master Degree In Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU -1998.Did PG Diploma In VLSI Design From V3 Logic Pvt Ltd B'Lore-2001, Did M.Tech (ECE) From IASE Deemed University-2005. Currently Pursuing (PhD)-ECE(VLSI), JNTU Hyderabad -2012, Over Past 16 years of Rich Professional Experience with Reputed IT Software Industrial

MNC's, Corporate -CYIENT (INFOTECH), ISiTECH as a world top keen IT Industrial Software Specialist - World Top Software Engineering Team Leader(Level 6) Eng-Eng-HCM Electronics Vertical & Program Manager – MFG I/C,EDS,BT,NON BT Embedded Software Avionics & Automotive Hi-tech Software Engineering Verticals & Departments Program Lead - Embedded & VLSI & Engineering Delivery Manager - IT Semiconductor Software Engineering Vertical , at ISiTECH, also worked with Govt R&D, **Industrial Organizations, Academic Institutions** of Comparative Designations & Rolls . His Areas Of Interest are VLSI -VHDL, Verilog HDL, ASIC, FPGA & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D ,Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, IT Software MNC Board Meetings(Tier1/2 Level MRM-VP,COO Level), Guided R&D, Industrial, Academic Projects / Products - VLSI-ASIC, FPGA & Embedded & Embedded, VLSI Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At CYIENT(INFOTECH) as a I/C- MFG Eng Software Vertical, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various national & International Journals.

G.Krishnaiah, Pursuing Ph.D from JNTU UNIVERSITY, Hyderabad, India. Currently working as a Professor, in the Department of Electronics and communication Engineering, Joginpally B.R Engineering college, Hyderabad, Telangana State, India. His carrier spans nearly 19 years in the field of teaching, administration, R&D, and Industry & Research. He has actively involved in organizing various conferences and work-shops. He has published over 4 international journal papers out of his research work. He

presented more than 3 Research papers at various national and International conferences. He is currently a Life Member of ISTE, IETE, CSI, and Member of IEEE and MIE. He is also guiding the projects of U.G / P.G. students of various universities. His area of Research includes Digital Signal Processing; Image & Video signal Processing, Low power VLSI Design, Embedded systems, Wireless communication, Global Positioning systems and Pseudolite Systems.

**Dr. D.N Rao B.Tech, M.E, Ph.D, principal** of JBREC, Hyderabad. His carrier spans nearly three decades in the field of teaching, administration, R&D, and other diversified in-depth experience in academics and administration. He has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international

conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities.

Dr.Vathsal Currently working as a Professor & Dean- R&D & EEE,JBIET,He Obtained PhD from I.I.S.C,Bangalore,also Did Post Doctoral Research in DFVLR,Germany and NASA Goddard Space Flight Centre,USA,and also he worked with keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He

Publised lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India.